SPI-Interface

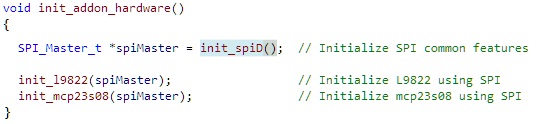

Das SPI-Modul (spiD_master.c) ist auf Port D als Master implementiert.

Prinzipieller Ablauf

Es können sich beliebig viele Device-Treiber als Master anmelden, da sie jeder ein eigenes Datenpaket verwalten. Auch können unterschiedliche Kontrollstrukturen, wie SPI-Mode und Clock-Frequenz parametriert werden. Während des Sendens einer SPI-Datenstroms wird kein zweites Senden zugelassen.

Das Senden wird per Aufruf gestartet und via Interrupt-Serviceroutine fortgesetzt. Beim Start wird das definierte SlaveSelect-Signal (CE) aktiviert.

Anschließend wird dem SPI-Modul des Prozessors das erste Datenbyte übergeben. Dadurch startet der Prozessor den Taktgenerator (CLK) mit der parametrierten Frequenz für genau dieses eine Byte, das auf der MOSI-Leitung erscheint. Zeitgleich - unter Nutzung des CLK-Signals - sendet das angeschlossene Device auf der MISO-Leitung ein entsprechenden Datum als Antwort an das SPI-Modul des Prozessors. Die CLK-Leitung ist immer nur während des Sendens auf MOSI- und MISO-Leitung aktiv.

Ist ein Byte vollständig gesendet, erzeugt der Prozessor einen Interrupt, in dessen Service-Routine das vom Device gesendete Datum gelesen werden kann. Jetzt wird geprüft, ob noch weitere Daten zu schreiben sind. Ist das der Fall, wiederholt sich der Sende-/Empfangszyklus (Tranceiving) wie beschrieben.

Nach dem Senden aller gewünschten Daten wird die SlaveSelect-Leitung deaktiviert. Damit ist die Operation abgeschlossen.

Zu beachten ist, dass der Empfang von Daten aus einem Device immer nur nach Senden von Informationen erfolgt.